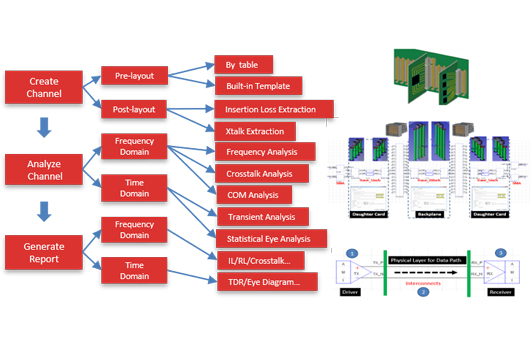

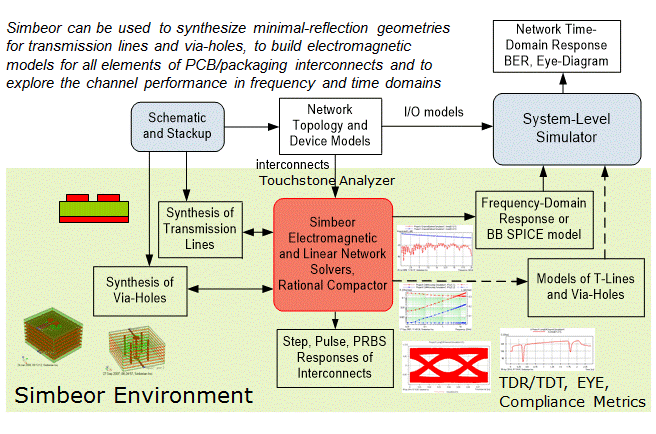

SIMBEOR是一个3D电磁信号完整性的工具,用于模拟和分析整个互连链接。它提供了一种电磁信号完整性软件,产业界首次使用measurement-validated PCB的物理设计和封装互联通信链路,可操作在6-112 Gb/s 或更高速率。Simbeor提供所有互连的一站式解决方案,用于预先仿真(先进的叠层规划和pre-layout),设计验证(布线后),介质和导体粗糙度模型识别、和宏观建模任务。模型的精度是保证通过使用先进的算法对3D三维全波分析,基准测试和实验验证。它适合任何设计系统的互连建模仿真探索工具,互连验证工具,或Touchstone模型清理和宏观模式下S参数自动提取的工具。

Simbeor 求解器和验算法:

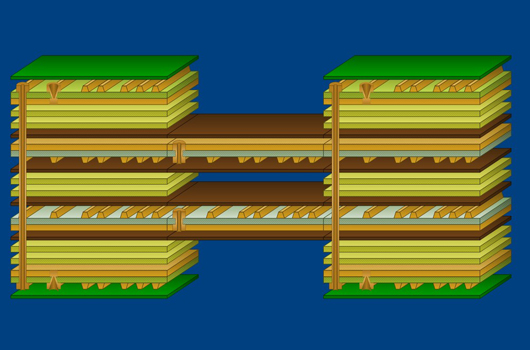

Simbeor 3DML™: 全波3D三维多层几何图形分析工具:

- 混合解算器:直线法+ Trefftz有限元素+同时对角线化(de-embedding)的方法

- 分析不连续和传输线路的高频(non-TEM)色散和各向异性(任何平面截面)

- Simbeor 3DTF™:第一个全波3D分析工具,基于Trefftz有限元素(即Ultra-Weak Discontinuous Galerkin's Wave Elements)

Simbeor SFS™: 独特的准静态场求解,用于大型t-line截面(任何平面截面):

- MoM:支持所有分散的各向同性材料和导体粗糙度模型

- 线性网络求解器:独特的端口电路分析与解决7个多端口网络的频率和时域分析,基于Y或S参数(对于非常大的多端口网络的稀疏求解器),功能提取GMS-parameters测试夹具的参数和de-embed测试夹具的能力

- Rational Compactor™:离散参数模型转换成frequency-continuous理性的宏观模型,进行一致的频率和时间域分析

只适用于大中国区、印度、越南、马来西亚、泰国和新加坡。zSimbeor : 工具和界面:

Board Analyzer™: 布线后的全局

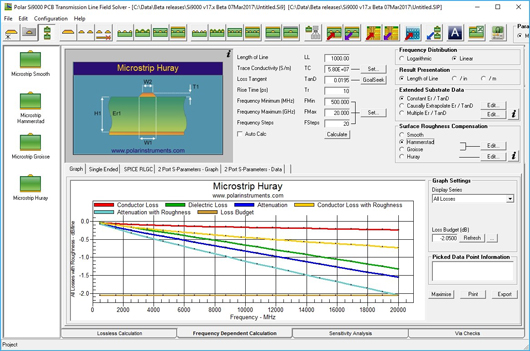

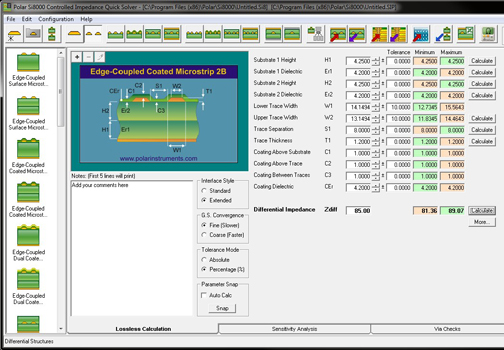

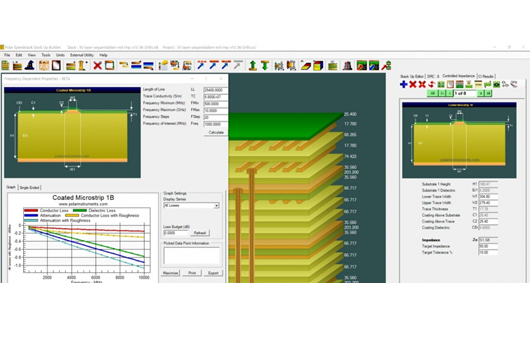

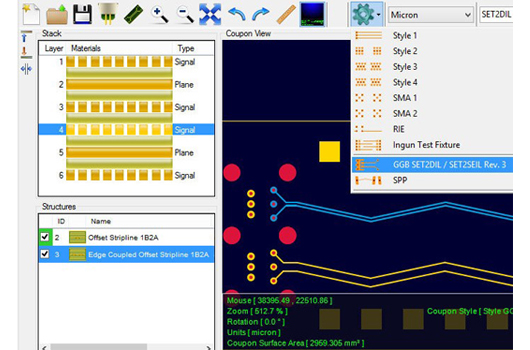

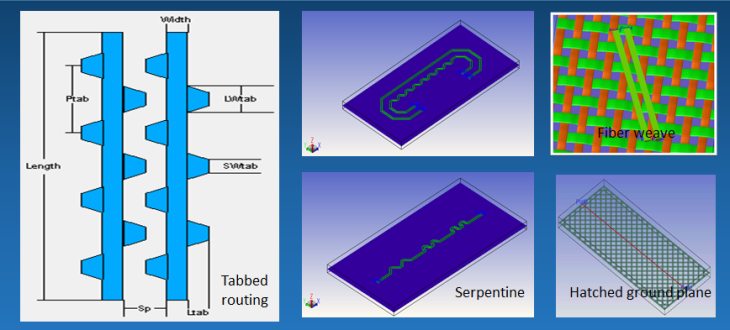

传输线路仿真—任何单端和差分线几何图形的快速合成(带,微带 ,CPW ,CBCPW)

Via Analyzer™: 快速合成via-holes并产生几何图形

Touchstone Analyzer™ : S参数绘图,质量保证和理性的宏观模式

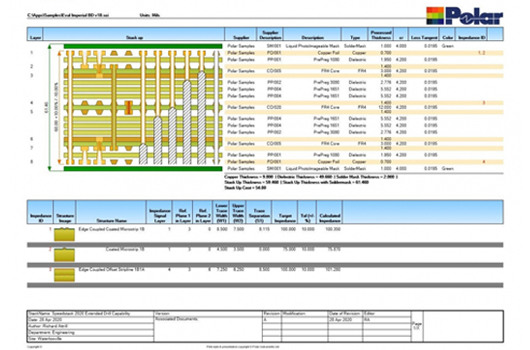

几何编辑: 布线前和多层电路布线后的分析

线性网络编辑: 绘制或编辑多端口网络(链接路径模型)

SiTune™: 材料模型、几何和线性网络的优化

电路板几何翻译: ODB++, HyperLynx hyp-file, Allegro brd/mcm, PADS ASCII

Violation Browser™: EMSAT规则检查的违规查看器

眼图分析仪™: 计算眼图的度量和比较眼图

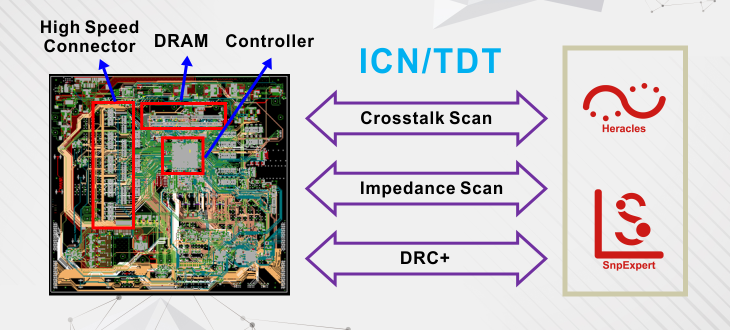

ICN分析仪™: 集成的串扰噪声和快速计算与合规的掩模的比较

交互式图表: 绘制传输线模态和RLGC (f)参数,S参数,10G和25 G合规指标, TDR/TDT,眼图

批处理模式—以批处理方式运行分析设计自动化

下载 SIMBEOR 手册

只适用于大中国区、印度、越南、马来西亚、泰国和新加坡。