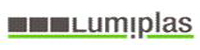

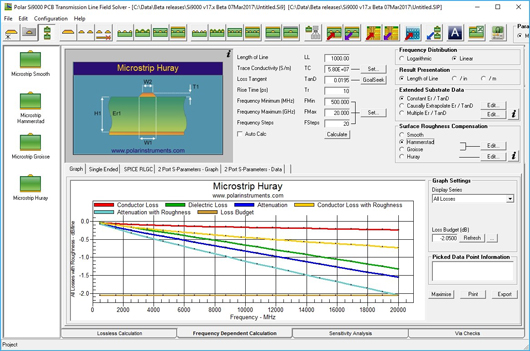

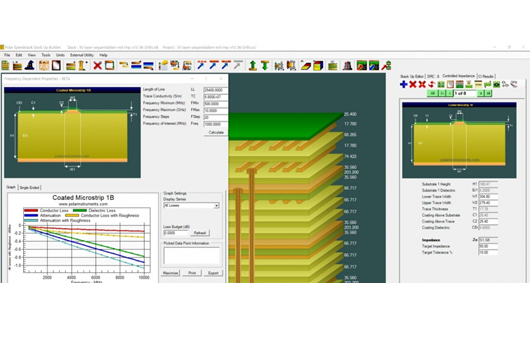

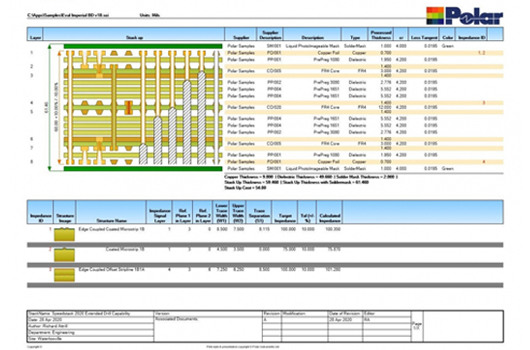

通过其快速,准确,与频率相关的传输线建模,Si9000e可以对传输线损耗,给定频率下的阻抗进行建模,并提取各种流行的PCB传输线(超过100种结构)中的完整传输线参数。Si9000e提取RLGC矩阵并针对要设计的结构快速绘制一系列传输线信息。损耗用三种方式绘制,清楚地表明了电介质,铜和总损耗,从2017年开始,包括用于粗糙度建模的Hammerstad,Groisse和Huray方法。

主要特点

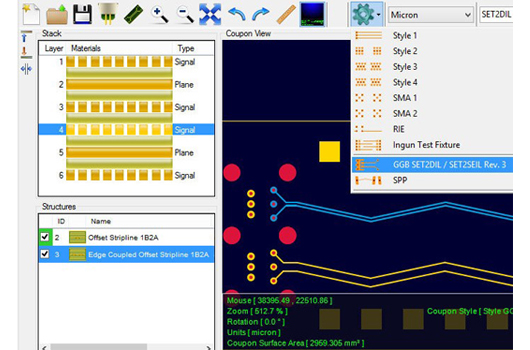

- 与Speedstack链接为Speedstack Si

- Si串扰选项–多线和差分对(无损)串扰–建模走线之间的耦合

- Speedstack的Si Projects选项可保存结构组

- 粗糙度建模–平滑/ Hammerstad / Groisse / Cannonball-Huray

- 内置阻抗图

- 绘制导体,电介质和插入损耗的图表

- 全面的S参数图一览-幅度,相位和史密斯圆图

- 单端和混合模式S参数图表和数据表

- 用户定义的S参数源和终端阻抗

- 频率依赖性建模低至1KHz

- 通过残桩孔检查进行/不进行

Si9000e选件

- XFE选项–为柔性和刚性刚性PCB提供交叉阴影线返回路径建模

- Si串扰选项–多线和差分对(无损)串扰–建模走线之间的耦合

- Si Excel界面选项– MicrosoftExcel®界面选项,用于Si9000e中的无损计算

- Speedstack Si的Si Projects选项Si保存结构组