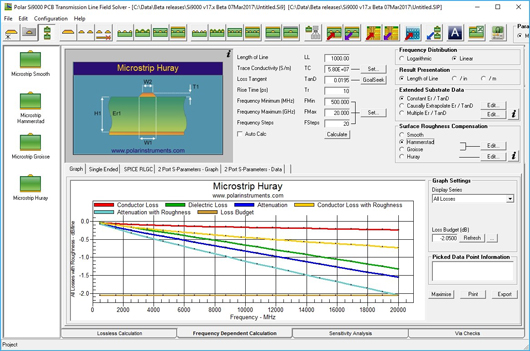

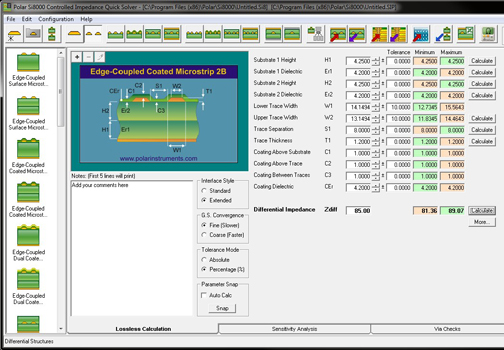

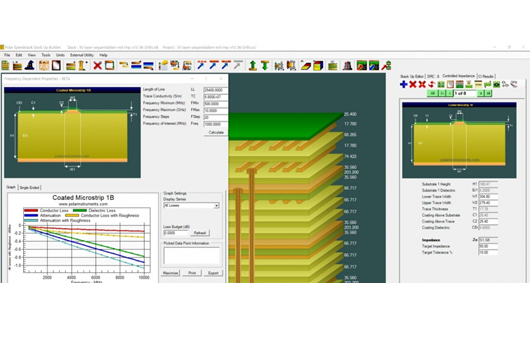

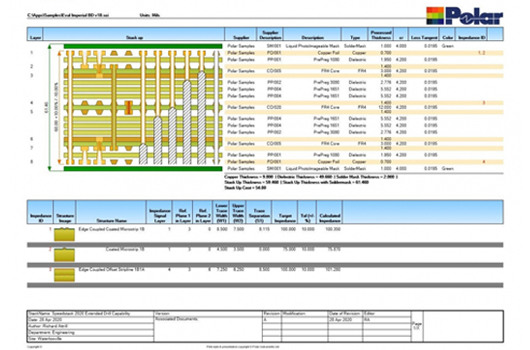

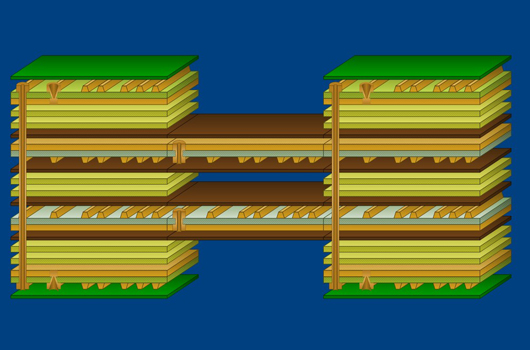

通過其快速,準確,與頻率相關的傳輸線建模,Si9000e可以對傳輸線損耗,給定頻率下的阻抗進行建模,並提取100多種結構的廣泛流行的PCB傳輸線上的完整傳輸線參數。 Si9000e提取RLGC矩陣,並為正在設計的結構快速繪製一系列傳輸線信息。 損耗用三種方式繪製,清楚地表明了介電質,銅和總損耗。 從2017年開始,包括用於銅(Cu)粗糙度建模的Hammerstad,Groisse和Huray方法。

Si9000e的主要特點

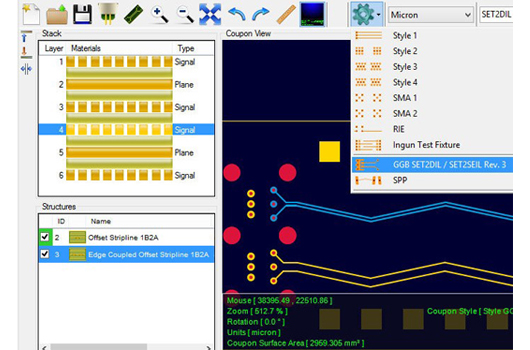

- 與Speedstack連接為Speedstack Si

- 粗糙度建模–Smooth/ Hammerstad / Groisse / Cannonball-Huray

- 內建阻抗圖

- 繪製導體,介電質和插入損耗的圖表

- 全面的S參數圖一覽-幅值,相位和史密斯圖

- 單端和混合模式S參數圖表和數據表

- 用戶定義的S參數源和終端阻抗

- 低至1KHz的頻率相關建模

- Go / No Go 盲埋孔檢查

Si9000e 選項

- XFE選項–為軟板和軟硬結合板提供網狀銅箔返迴路徑建模

- Si串擾選項–多線和差分對(無損)串擾–建模走線之間的耦合

- Si Excel界面選項– MicrosoftExcel®界面選項,用於Si9000e中的無損計算

- Speedstack Si的Si Projects選項可保存結構群組

下載Si9000e手冊